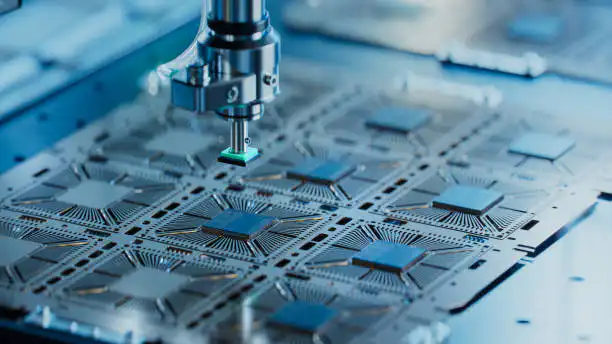

Wraz z tym, jak miniaturyzacja chipów zbliża się do fizycznych granic, tradycyjne procesy produkcyjne nie są już w stanie zapewniać wzrostu wydajności jedynie poprzez zmniejszanie szerokości linii. Aby utrzymać wzrost mocy obliczeniowej i efektywności energetycznej, uwaga branży stopniowo przesuwa się w stronę technologii Zaawansowanego Pakowania (Advanced Packaging).

Dzięki wprowadzeniu połączeń o wysokiej gęstości i 3D stackingu między układami scalonymi, zaawansowane obudowy mogą osiągnąć wysoką prędkość transmisji, niskie zużycie energii i wysoki poziom integracji bez konieczności zmiany architektury układów scalonych. Spośród nich technologia CoWoS jest najbardziej reprezentatywnym rozwiązaniem w zakresie wysokowydajnych obudów w ostatnich latach i doprowadziła do powstania wielu rozszerzonych form, takich jak CoPoS i CoWoP, które stanowią główny kierunek rozwoju technologii obudów nowej generacji.

Tabla de contenido

Podstawy technologii CoWoS: Podstawy integracji 2,5D y 3D

CoWoS (Chip-on-Wafer-on-Substrate) to architektura pakowania o wysokiej gęstości, której centralnym elementem jest Warstwa Pośrednia (Interposer).

Koncepcja projektowa polega na tym, że wiele układów scalonych (chipów) jest najpierw układanych w stosy i łączonych ze sobą na etapie wafla krzemowego, a następnie jako całość montowanych na podłożu (基板). Taka struktura pozwala na skrócenie dystansu transmisji sygnałów, przy jednoczesnym obniżeniu poboru mocy i zmniejszeniu wymiarów systemu.

En función de los diferentes materiales utilizados en la capa intermedia y los métodos de interconexión, la tecnología CoWoS se puede dividir en tres categorías principales:

- CoWoS-S: Emplea un interponedor de silicio que ofrece la mayor densidad de conductividad y capacidad de integración, lo que lo hace adecuado para aplicaciones de computación de alto rendimiento.

- CoWoS-R: Sustituye los interconectores de silicio por capas de recableado (RDL), lo que reduce los costes de procesamiento y aumenta la flexibilidad de diseño.

- CoWoS-L: Un diseño híbrido de silicio y RDL que combina alto rendimiento y rentabilidad, permitiendo apilar más chips y memoria.

CoWoS-L se considera un punto de equilibrio en la arquitectura existente, ya que supera las limitaciones del área del interponedor al tiempo que mantiene una transmisión de señal de alta velocidad y un buen rendimiento de disipación de calor.

CoPoS: Embalaje basado en paneles, que marca el comienzo de una nueva era de «sustitución de lo redondo por lo cuadrado».

A medida que el tamaño de los chips de IA y computación de alto rendimiento sigue aumentando, la utilización del área y la capacidad de producción de las obleas circulares tradicionales se ven gradualmente limitadas. Para abordar este problema, ha surgido el concepto de empaquetado a nivel de panel CoPoS (Chip-on-Panel-on-Substrate).

CoPoS utiliza una «capa RDL de panel» cuadrada en lugar de un interpositor de oblea circular; los chips pueden disponerse directamente sobre el sustrato rectangular y conectarse a la placa base portadora mediante el proceso de encapsulado. Este diseño no solo mejora la tasa de utilización del área y la eficiencia de producción, sino que también permite integrar chips de diferentes tamaños, reduciendo el alabeo del empaque y los problemas de rendimiento.

Además, los paneles pueden utilizar materiales altamente estables como vidrio o zafiro, lo que mejora la disipación del calor y reduce la deformación.

Actualmente, los tamaños más comunes son 310 × 310 mm, 515 × 510 mm y 750 × 620 mm, lo que está impulsando gradualmente el proceso de empaquetado, pasando de formatos redondos a cuadrados, y convirtiéndose en una tendencia predominante en la era posterior a la Ley de Moore.

Cabe destacar que, si bien CoPoS y FOPLP (Fan-out Panel Level Packaging) pertenecen al empaquetado a nivel de panel, su posicionamiento es claramente diferente:

- CoPoS se utiliza para la integración de chips e interponedores de alto rendimiento.

- La tecnología FOPLP se utiliza principalmente en aplicaciones de gama baja a media, como chips de administración de energía y chips de RF, y no requiere una estructura de capa intermedia.

CoWoP: Innowacyjne podejście mające na celu dalsze uproszczenie warstwy pakowania.

A diferencia de la búsqueda de la panelización de CoPoS, el objetivo de CoWoP(Chip-on-Wafer-on-Platform PCB) es simplificar la estructura del nivel de empaque. En la estructura tradicional de CoWoS, la conexión entre los chips y los módulos de memoria debe realizarse capa por capa a través de interpositores, sustratos de empaque y esferas de soldadura BGA hasta llegar a la placa base, lo que resulta en una estructura compleja y una acumulación de costos.

CoWoP, por su parte, omite directamente el sustrato de empaque y las esferas BGA, utilizando en su lugar una placa base PCB(Platform PCB) con capacidad de interconexión de alta precisión como capa portadora, permitiendo que el interpositor y los módulos de chips se instalen directamente sobre el PCB.

Este método permite acortar la ruta de transmisión de la señal, mejorar la integridad de la misma y optimizar tanto la disipación de calor como la eficiencia del suministro eléctrico.

Si esta tecnología se produce en masa con éxito, podría redefinir la frontera entre el embalaje y las placas de circuitos impresos, y aportar cambios significativos al diseño de la arquitectura de sistemas de alto rendimiento.

WMCM: Inna ścieżka integracji wieloprocesorowej na poziomie wafli

Además de las tecnologías mencionadas anteriormente, WMCM (Módulo Multichip a Nivel de Oblea) es otra nueva dirección de empaquetado que merece mención. Esta tecnología puede considerarse una forma de integración a nivel de oblea, que representa una extensión planarizada del empaquetado tradicional.

WMCM ya no utiliza el apilamiento vertical de chips. En su lugar, integra los chips lógicos y los planos de memoria en el mismo nivel de oblea y reemplaza el interposer con una estructura RDL. Este diseño permite mejorar simultáneamente los cuellos de botella térmicos y la latencia de la señal, además de simplificar el grosor y el coste del encapsulado.

Dado que toda la integración se completa en la etapa de oblea, y luego las obleas se cortan en chips individuales, se puede lograr una estructura de módulo multichip más delgada y eficiente.

Desde la innovación en el embalaje hasta la integración de sistemas

Desde CoWoS a CoPoS, y luego a CoWoP y WMCM, se puede observar que la idea central de la tecnología de empaquetado está pasando del «apilamiento de chips» a la «integración de sistemas».

La aparición de diferentes arquitecturas refleja la diversidad de soluciones que la industria ofrece para afrontar desafíos como el rendimiento, la productividad, la disipación de calor y el coste. En el futuro, con la profundización de la integración heterogénea y la especialización de chips, el empaquetado avanzado se convertirá en una tecnología clave para mantener vivo el espíritu de la Ley de Moore.

Quien domine los materiales, procesos y capacidades de diseño clave en esta revolución del empaquetado podrá dominar el futuro de los chips de alto rendimiento en la era del postprocesamiento.

Referencias:

- CoWoS、CoPoS、CoWoP 傻傻分不清,誰才是下一代最該關注的技術?

En términos de molienda, ofrecemos ajustes personalizados y podemos ajustar la proporción según los requisitos de procesamiento para lograr la máxima eficiencia.

Bienvenido a contactarnos, tendremos alguien para responder sus preguntas.

Si necesita un presupuesto personalizado, póngase en contacto con nosotros.

Horario de atención al cliente: lunes a viernes de 09:00 a 18:00

Teléfono: 07 223 1058

Si tienes alguna duda o pregunta sobre el número de teléfono, no dudes en enviar un mensaje privado a Facebook~~

Facebook de Honway: https://www.facebook.com/honwaygroup

Artículos que te pueden interesar…

[wpb-random-posts]